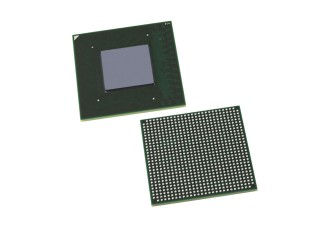

EP2AGX125EF29C6N

- Product Code: EP2AGX125EF29C6N

- Availability: In Stock

[ALTERA]

Overview for the Arria II Device Family

The Arria® II device family is designed specifically for ease-of-use. The cost-optimized, 40-nm device family architecture features a low-power, programmable logic engine and streamlined transceivers and I/Os. Common interfaces, such as the Physical Interface for PCI Express® (PCIe®), Ethernet, and DDR3 memory are easily implemented in your design with the Quartus® II software, the SOPC Builder design software, and a broad library of hard and soft intellectual property (IP) solutions from Altera. The Arria II device family makes designing for applications requiring transceivers operating at up to 6.375 Gbps fast and easy.

Arria II Device Feature

The Arria II device features consist of the following highlights:

■ 40-nm, low-power FPGA engine

■ Adaptive logic module (ALM) offers the highest logic efficiency in the industry

■ Eight-input fracturable look-up table (LUT)

■ Memory logic array blocks (MLABs) for efficient implementation of small FIFOs

■ High-performance digital signal processing (DSP) blocks up to 550 MHz

■ Configurable as 9 x 9-bit, 12 x 12-bit, 18 x 18-bit, and 36 x 36-bit full-precision multipliers as well as 18 x 36-bit high-precision multiplier

■ Hardcoded adders, subtractors, accumulators, and summation functions

■ Fully-integrated design flow with the MATLAB and DSP Builder software from Altera

■ Maximum system bandwidth

■ Up to 24 full-duplex clock data recovery (CDR)-based transceivers supporting rates between 600 Mbps and 6.375 Gbps

■ Dedicated circuitry to support physical layer functionality for popular serial

protocols, including PCIe Gen1 and PCIe Gen2, Gbps Ethernet, Serial

RapidIO® (SRIO), Common Public Radio Interface (CPRI), OBSAI,

SD/HD/3G/ASI Serial Digital Interface (SDI), XAUI and Reduced XAUI

(RXAUI), HiGig/HiGig+, SATA/Serial Attached SCSI (SAS), GPON,

SerialLite II, Fiber Channel, SONET/SDH, Interlaken, Serial Data Converter

(JESD204), and SFI-5.

■ Complete PIPE protocol solution with an embedded hard IP block that provides physical interface and media access control (PHY/MAC) layer, Data Link layer, and Transaction layer functionality

■ Optimized for high-bandwidth system interfaces

■ Up to 726 user I/O pins arranged in up to 20 modular I/O banks that support a wide range of single-ended and differential I/O standards

■ High-speed LVDS I/O support with serializer/deserializer (SERDES) and dynamic phase alignment (DPA) circuitry at data rates from 150 Mbps to 1.25 Gbps

■ Low power

■ Architectural power reduction techniques

■ Typical physical medium attachment (PMA) power consumption of 100 mW at 3.125 Gbps.

■ Power optimizations integrated into the Quartus II development software

■ Advanced usability and security features

■ Parallel and serial configuration options

■ On-chip series (RS) and on-chip parallel (RT) termination with auto-calibration for single-ended I/Os and on-chip differential (RD) termination for differential I/O

■ 256-bit advanced encryption standard (AES) programming file encryption for design security with volatile and non-volatile key storage options

■ Robust portfolio of IP for processing, serial protocols, and memory interfaces

■ Low cost, easy-to-use development kits featuring high-speed mezzanine connectors (HSMC)

■ Emulated LVDS output support with a data rate of up to 1152 Mbps